Engineering Portfolio

A portfolio of things I’ve designed, implemented, and debugged.

- Building PixelForge retro graphics engine on Basys3

- Studying memory systems + architecture

- Seeking summer hardware/software engineering internships 2026

Projects

PixelForge — FPGA Retro Graphics Engine (Basys3 / Artix-7)

SystemVerilog • VGA 640×480@60Hz • BRAM • SVA • ILA

PixelForge — FPGA Retro Graphics Engine (Basys3 / Artix-7)

SystemVerilog • VGA 640×480@60Hz • BRAM • SVA • ILA

Built an FPGA retro graphics engine (sprite + tilemap renderer) and demoed real-time VGA output on Basys3. Implemented a pipelined pixel path and closed post-route timing; validated with a self-checking testbench, SVA assertions, and on-board ILA debug.

- Implemented SV VGA timing + pipelined pixel path; closed post-route timing (WNS +1.3 ns @ 100 MHz)

- BRAM-backed tile/sprite compositor; ~2.1k LUT / 2.6k FF / 8 BRAM, Fmax ~165 MHz

- Self-checking SV testbench + SVA (~120 asserts) + on-board ILA debug; fixed 6 corner bugs pre-bitstream

SpeakUp — Real-Time Sign Language to Speech Translator

Raspberry Pi 3 • Sony IMX500 • TensorFlow • Quantization • eSpeak TTS

SpeakUp — Real-Time Sign Language to Speech Translator

Raspberry Pi 3 • Sony IMX500 • TensorFlow • Quantization • eSpeak TTS

Built an embedded ASL-to-speech translator on Raspberry Pi 3 + Sony IMX500 for fully offline use. Achieved real-time inference with low end-to-end latency on resource-constrained hardware, then optimized the capture → NN → TTS pipeline with pipelining + thread pinning.

- Fine-tuned & quantized MobileNetV2 (TensorFlow) for gesture recognition (~91% accuracy)

- Integrated recognition with eSpeak TTS (~250 ms time-to-first audio; ~120 ms audio lag)

- Optimized pipeline with pipelining & thread pinning (CPU <70%, RAM <220 MB, power ≤3.2 W)

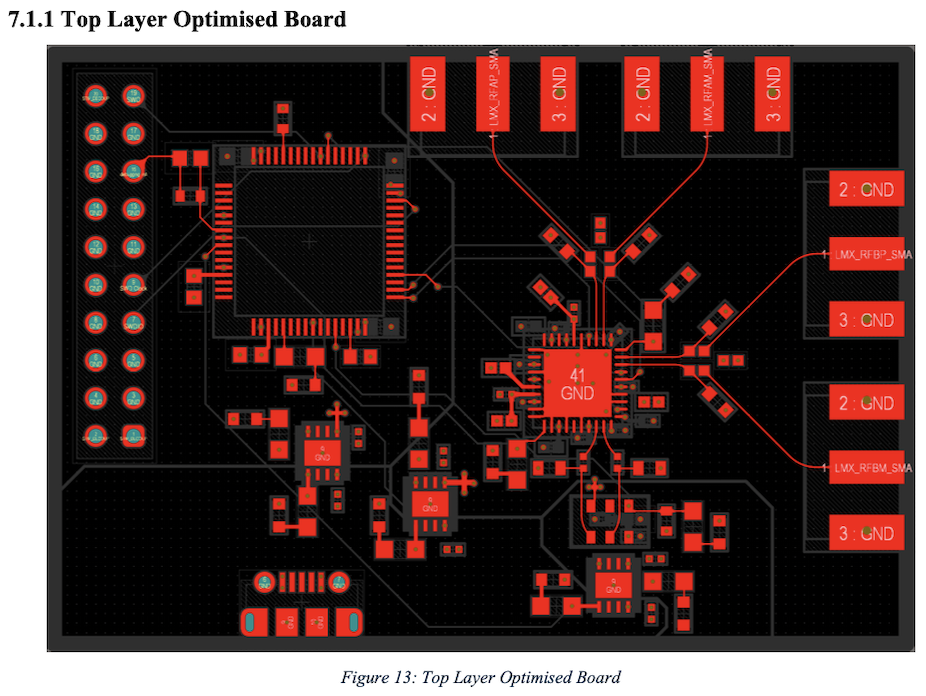

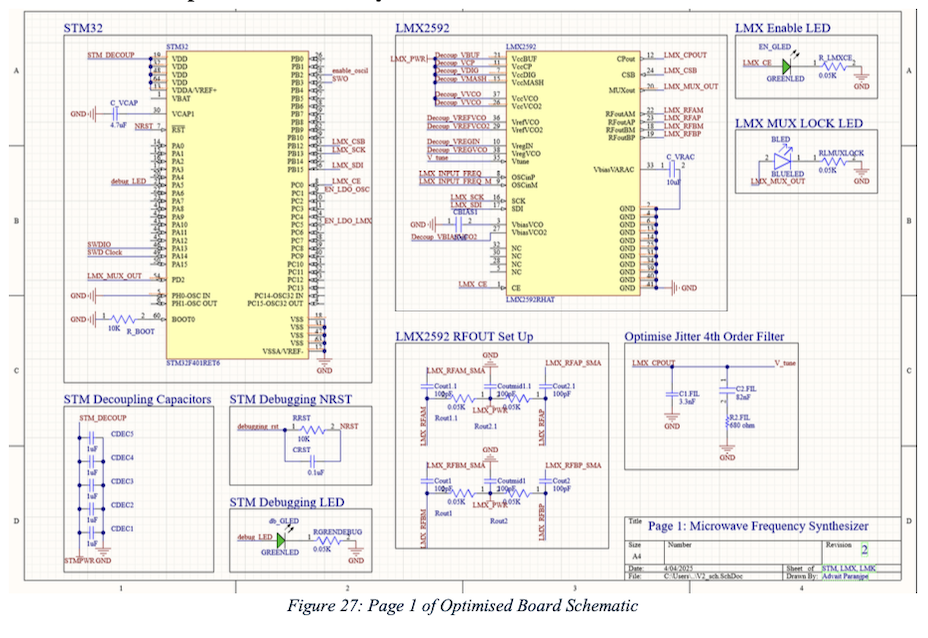

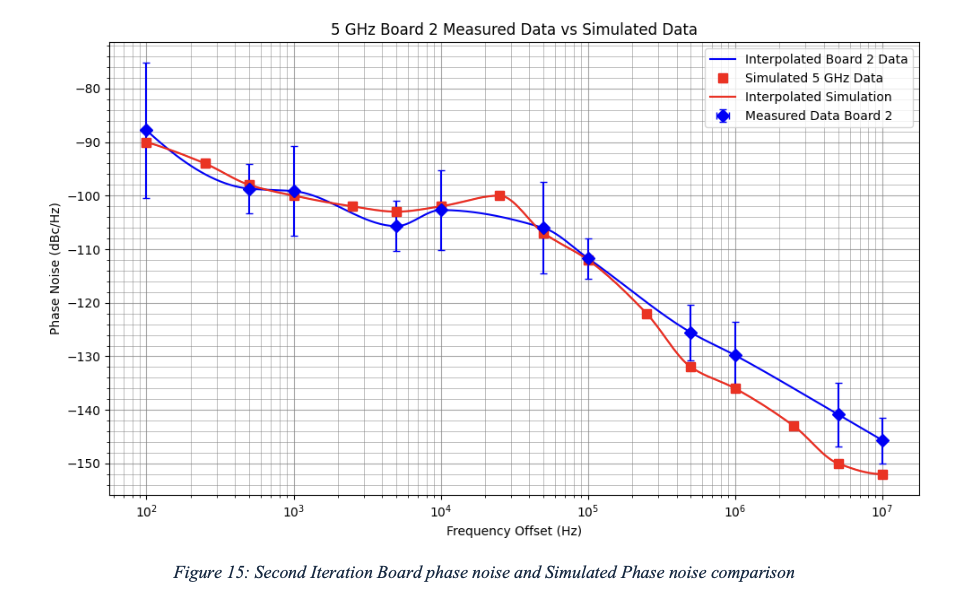

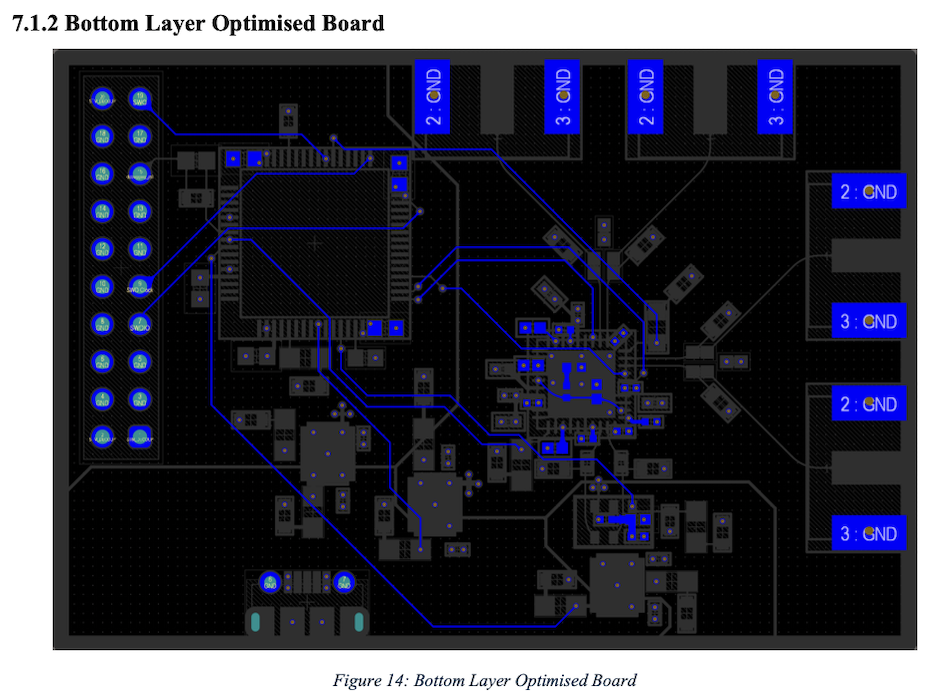

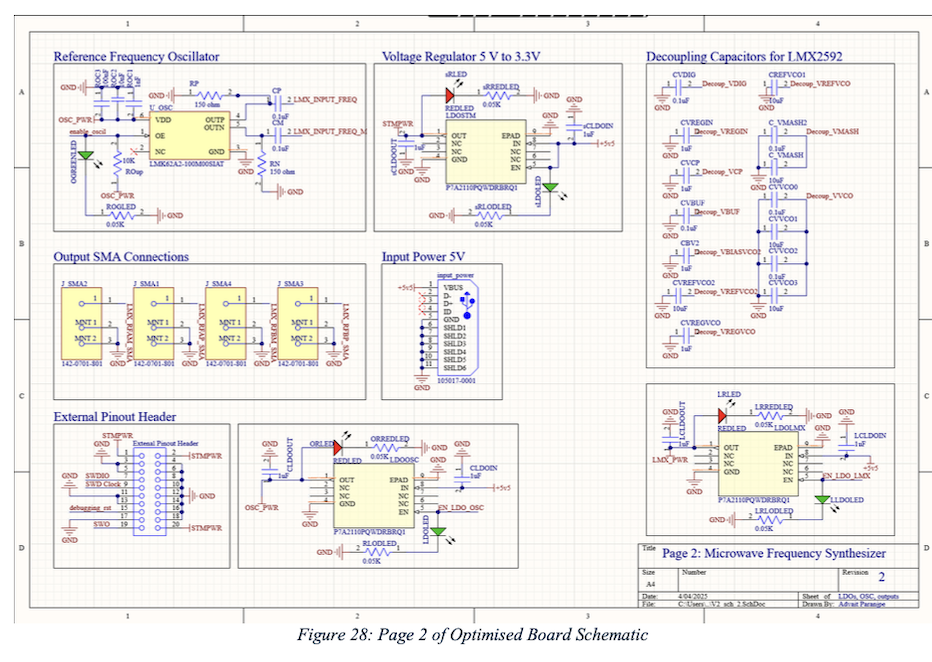

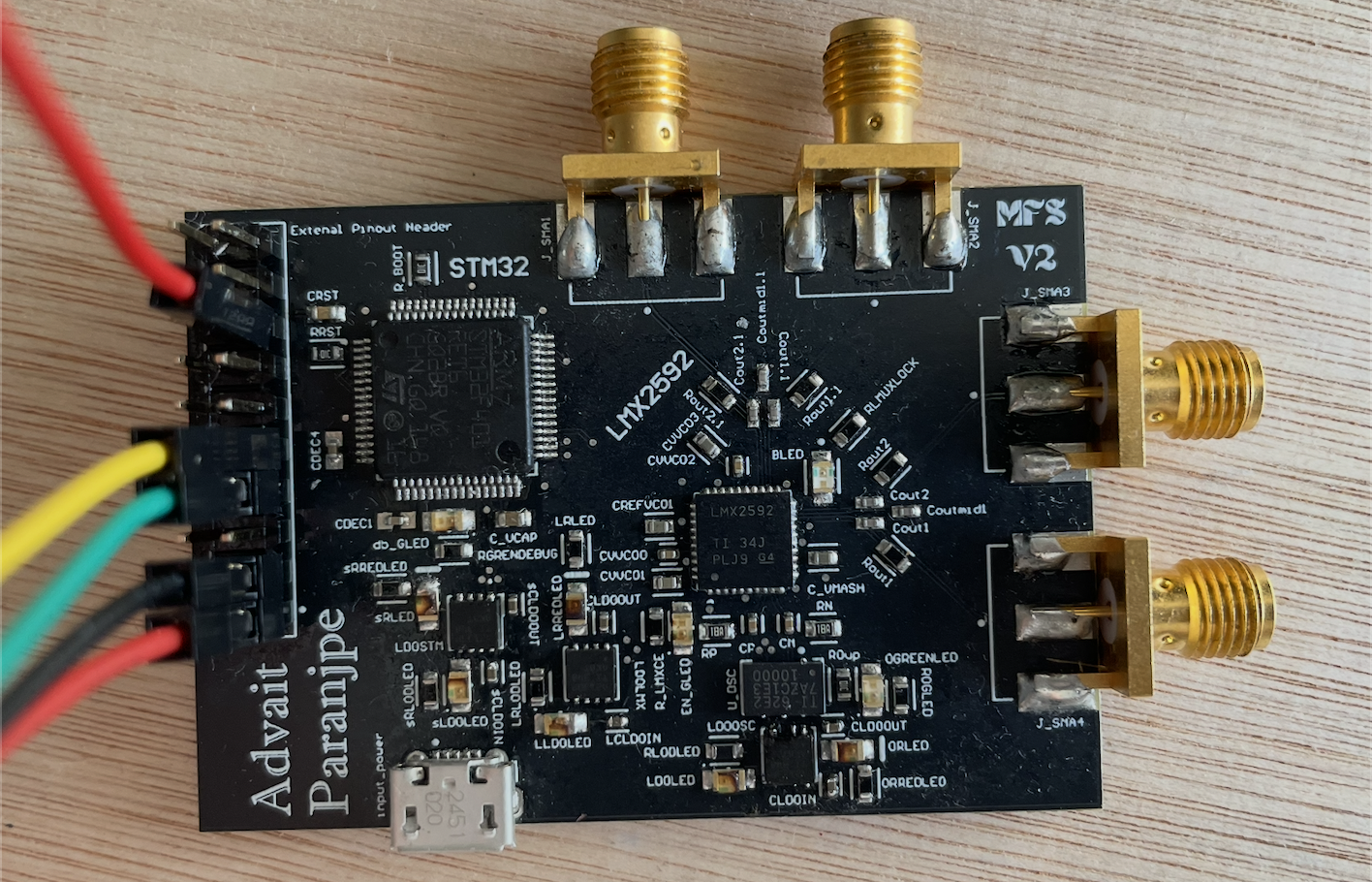

Dissertation — Novel Tunable Microwave Frequency Synthesizer (Cascaded PLL)

RF PCB • Cascaded PLL • SPI (CRC + readback) • Firmware • Python GUI • Lab validation

Dissertation — Novel Tunable Microwave Frequency Synthesizer (Cascaded PLL)

RF PCB • Cascaded PLL • SPI (CRC + readback) • Firmware • Python GUI • Lab validation

Architected a 5G synthesizer with a novel cascaded-PLL topology and validated the design using a spectrum analyzer.

Specified a register map + CRC-protected SPI protocol with read-back verification (RTL/FPGA-ready interface),

and built firmware + a Python GUI to enable fast switching and calibration.

- Outperformed TI eval-board limits by 20 dBc/Hz (lab-validated on spectrum analyzer)

- Delivered first-pass SI by enforcing controlled impedance + robust PDN decoupling

- Implemented C/C++ firmware + Python GUI; switching under 1 s; 3× faster calibration

- Next: add measurement plots (phase noise) + block diagram + register-map excerpt

Media

Measurements, PCB, and tooling snapshots.

STMicroelectronics — Autonomous Line Tracking Buggy

C++ • PID control • Embedded sensing/actuation • Competition build

STMicroelectronics — Autonomous Line Tracking Buggy

C++ • PID control • Embedded sensing/actuation • Competition build

Built an autonomous line-tracking buggy and developed a PID controller for robust tracking performance. Tuned the control loop to maintain stability across track variation and sensor noise.

- Developed a PID controller achieving 100% line-tracking accuracy

- Placed top 3 among 50+ teams

Experience

National Energy System Operator — Backend Software Engineering Intern

Python • Vectorization • Bayesian decision engine • APIs • Parallelism

National Energy System Operator — Backend Software Engineering Intern

Python • Vectorization • Bayesian decision engine • APIs • Parallelism

Performance-focused refactors and pipeline improvements for forecasting/simulation tooling at scale. Emphasis on correctness, reliability, and measurable speedups.

- Refactored a critical 100k+ LOC tool with vectorization → 10× faster daily run (450+ hrs/year saved)

- Built a Bayesian decision engine → 60× faster price-forecasting runs (investment risk insights)

- Parallelized + batched API requests → 24× faster simulation-input pipeline

- Chunked parallelization for 100M+ rows → RAM 32→16 GB and 11× faster execution

National Grid ESO — Data Engineering Intern

Python • Pandas/NumPy • API integration • Data pipelines

National Grid ESO — Data Engineering Intern

Python • Pandas/NumPy • API integration • Data pipelines

Built and improved data ingestion/processing pipelines for grid datasets, with a focus on automation, performance, and stakeholder-friendly outputs.

- Integrated the Elexon API into a Python service to keep bid/offer values up to date (400+ hrs/year saved)

- Designed a grid data processing pipeline using Pandas and NumPy (+40% parsing efficiency)

- Translated 100M+ data points into intuitive stakeholder-facing formats for faster reviews/decisions

BMW — Electronics and Systems Technology Intern

C++ • Tooling • Diagnostics • Infotainment systems

BMW — Electronics and Systems Technology Intern

C++ • Tooling • Diagnostics • Infotainment systems

Worked on tooling support for diagnostics workflows on the MGU22 infotainment platform, contributing to shorter test cycles for regenerative-braking diagnostics.

- Helped build C++ tooling for the MGU22 infotainment platform for regenerative-braking diagnostics

About

I’m a UCLA M.S. ECE student who likes building real projects and getting them to work end-to-end. I care about clear design, careful debugging, and having something concrete to show: tests, measurements, demos, or benchmarks.